# TOWSON UNIVERSITY OFFICE OF GRADUATE STUDIES

## MULTI-CORE IMPLEMENTATION FOR BARE MACHINE COMPUTING

by

**Hojin Chang**

**A Dissertation**

Presented to the faculty of

**Towson University**

in partial fulfillment

of the requirements for the degree

**Doctor of Science**

**Department of Computer & Information Sciences**

**Towson University**

Towson, Maryland 21252

**August**, 2017

© 2017 by Hojin Chang All Rights Reserved

## TOWSON UNIVERSITY OFFICE OF GRADUATE STUDIES

#### DISSERTATION APPROVAL PAGE

This is to certify that the dissertation prepared by Hojin Chang, entitled "MIJITT-CORE IMPLEMENTATION FOR BARF MACHINE COMPUTING," has been approved by the dissertation committee as satisfactorily completing the dissertation requirements for the degree Doctor of Science in Information Technology.

| Chair, Dissertation Committee, Dr. Ramesh K. Karne                         | 7-27-17<br>Date   |

|----------------------------------------------------------------------------|-------------------|

| Committee member, Dr. Alexander L. Wijesinhp                               | 7/27/17<br>Date   |

| Zolongaung Charles Committee member. Dr. Sungehal Hong                     | 7/27/17<br>Date   |

| Committee member, Dr. Ziying Tang                                          | 721/2017          |

| Doctoral Program Director, Dr. Chao Lu                                     | 7/27/2017<br>Date |

| Chair, Department of Computer and Information Sciences. Dr. Siddbarth Kaza | 7/27/17<br>Date   |

| Janet V Dehony<br>Dean of Graduate Studies                                 | 8:01-17<br>Date   |

## Acknowledgements

I would like to express my appreciation to all those who have supported my efforts to complete this dissertation. I am greatly appreciative of my research committee Dr. Ramesh K. Karne (Chair), Dr. Alexander Wijesinha (Co-chair), Dr. Sungchul Hong, and Dr. Ziying Tang for supporting this research. I am especially thankful to Dr. Karne and Dr. Wijesinha for all the long hours in lab especially in many weekends for their support and advice. Also, I give all glory and honor to my GOD and offer my heartfelt thanks to my beloved parents who are Jaeyoung Chang and JungSoon Yang, whose words have encouraged me to complete my doctoral study.

Many thanks also go to Dr. Chao Lu, Doctoral Program Director of the Department of Computer and Information Sciences at Towson University, for facilitating this work. I am also grateful to the late Frank Anger (National Science Foundation) for his support of the Application Oriented Object Architecture (AOA), which evolved into Bare Machine Computing research and consequently made this dissertation possible.

#### Abstract

#### MULTI-CORE IMPLEMENTATION FOR BARE MACHINE COMPUTING

## Hojin Chang

This dissertation extends on-going Bare Machine Computing (BMC) research at Towson University. BMC applications run on a bare machine without any commercial operating system, kernel, or any other centralized support. This dissertation will serve as a cornerstone for future multi-core systems that run on bare machines.

Multi-core processors are deployed on most desktops, laptops and other devices. Since the inception of BMC, applications were implemented on a 32-bit single core Intel architecture (x86) due to its availability and skill set in the BMC laboratory. The multicore architecture coupled with 64-bit CPUs poses numerous challenges in implementing bare machine computing applications. This thesis lays a foundation to understand the design issues in implementing and porting existing applications to 64-bit multi-core architecture. First, the existing boot and load programs for BMC are ported to run in the new platform. This posed numerous problems due to architectural differences in 32-bit and 64-bit architectures. Second, some existing applications are ported to run on the new platform. A Web server application written for a 32-bit architecture is made to run on the new platform. This step is involved in a variety of architectural and design issues and incompatibilities among the old and new architectures. Finally, the Web server is made to run on multi-core by scheduling its threads to multiple cores. This posed a daunting challenge due to its complexity, some preliminary work in this area has been completed and the rest is left for future explorations.

This dissertation developed a variety of tools and techniques that are useful for future research in BMC applications. As the current technology is moving towards multi-core CPUs, it is necessary to study this problem for BMC applications. It has been discovered that the 32-bit and 64-bit architectural differences pose major difficulties in porting existing applications to smoothly run 64-bit multi-core architecture, whether they are conventional or bare.

## **Table of Contents**

| L | ist of tables                                                                     | ix   |

|---|-----------------------------------------------------------------------------------|------|

| L | ist of figures                                                                    | X    |

| 1 | MOTIVATION                                                                        | 1    |

| 2 | INTRODUCTION                                                                      | 2    |

| 3 | RELATED WORK                                                                      | 4    |

|   | 3.1 Bare Machine Computing Background                                             |      |

|   | 3.2 BMC Applications                                                              |      |

|   | 3.3 Other Related Work                                                            |      |

| 4 | INSIGHT INTO x86_64 BARE PC METHODOLOGY                                           | 9    |

|   | 4.1 Overview                                                                      |      |

|   | 4.2 Methodology                                                                   |      |

|   | 4.3 BOOT/LOAD/RUN PROGRAM PROCESS                                                 |      |

|   | 4.3.1 Boot Program                                                                |      |

|   | 4.3.3 Mass Storage and Memory Layouts                                             |      |

|   | 4.3.4 USB Image Maker                                                             |      |

|   | 4.4 BOOT/LOAD/RUN IMPLEMENTATION AND API                                          |      |

|   | 4.5 FUNCTIONAL OPERATION AND TESTING                                              | . 22 |

|   | 4.6 NOVEL FEATURES                                                                |      |

| _ | 4.7 SUMMARY                                                                       |      |

| 5 | Migrating a Web Server to a Multi-core Architecture                               |      |

|   | 5.1 BASIC ISSUES IN MIGRATION                                                     |      |

|   | 5.2 PAGING AND SINGLE CORE                                                        |      |

|   | 5.3 MULTICORE MIGRATION                                                           |      |

|   | 5.3.2 AP Flow                                                                     |      |

|   | 5.3.3 Task Scheduling Flow                                                        |      |

|   | 5.4 FUNCTIONAL OPERATION AND DATA                                                 |      |

|   | 5.4.1 First Migration Attempt                                                     | . 48 |

|   | 5.4.2 Single Core with Paging                                                     |      |

|   | 5.4.3 Multi-Core                                                                  |      |

|   | 5.5 DISCUSSION                                                                    |      |

| 6 | 5.6 SUMMARY                                                                       |      |

| U |                                                                                   |      |

|   | 6.1 BMC Tasking                                                                   |      |

|   | <ul><li>6.2 Scheduling</li><li>6.3 Existing Inter-Process Communication</li></ul> |      |

|   | 6.4 Multi-core Inter-Process Communication                                        |      |

| 7 | Conclusion                                                                        |      |

| A | Appendix                                                                          | . 60 |

|   |                                                                                   |      |

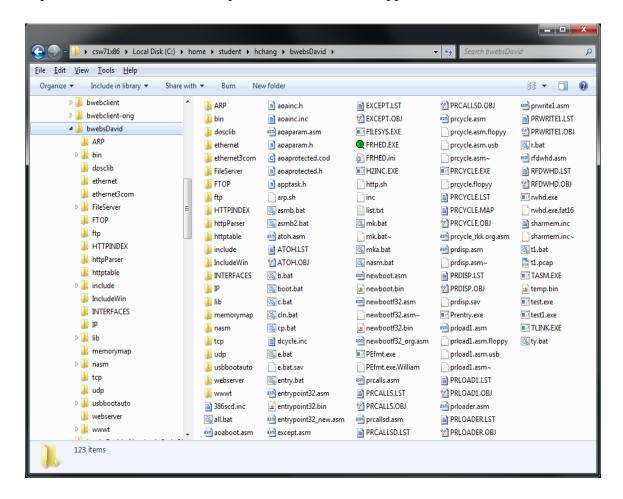

| A.  | Directory Structure           | 60 |

|-----|-------------------------------|----|

| B.  | Compilation Environment       | 61 |

| C.  | Debugging Process             | 63 |

| D.  | User's Guide and Screen Shots | 64 |

| Ref | ferences                      | 69 |

| Cur | rriculum Vitae                | 74 |

## LIST OF TABLES

| Table 1: OS-Based System VS. Bare Machine System | able 1: | VS. Bare Machine System |  |

|--------------------------------------------------|---------|-------------------------|--|

|--------------------------------------------------|---------|-------------------------|--|

## LIST OF FIGURES

| Figure 1: Methodology                                    | 10 |

|----------------------------------------------------------|----|

| Figure 2: 64-bit Specifics                               | 11 |

| Figure 3: USB Layout                                     | 15 |

| Figure 4: Memory Layout                                  | 17 |

| Figure 5: EntryPoint32                                   | 19 |

| Figure 6: Main.c (first Main())                          | 19 |

| Figure 7: Entrypoint64.s (64-bit Entrance assembly code) | 20 |

| Figure 8: Main.c (second main() for 64-bit)              | 21 |

| Figure 9: Selected Interfaces Details                    | 22 |

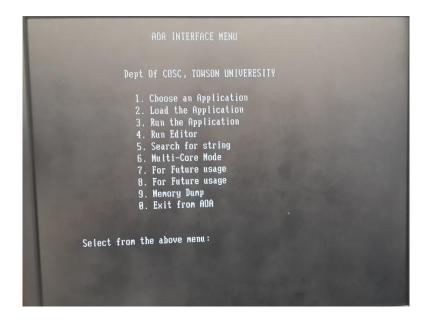

| Figure 10: Menu Interface                                | 23 |

| Figure 11: Application Output                            | 23 |

| Figure 12: Image Maker Trace                             | 24 |

| Figure 13: 4K Paging                                     | 27 |

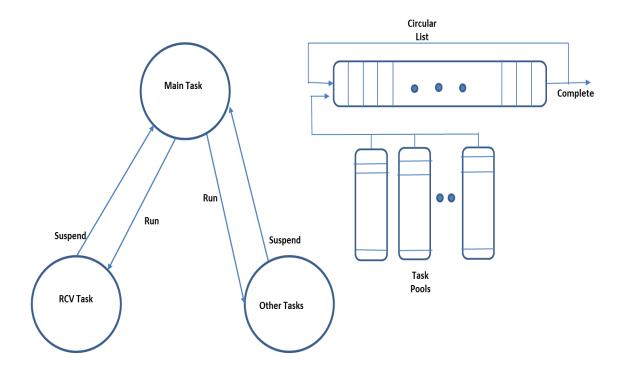

| Figure 14: Current Webserver Architecture                | 29 |

| Figure 15: BSP Flow (1E)                                 | 30 |

| Figure 16: GDT, IDT                                      | 33 |

| Figure 17: MP Configuration Structure                    | 34 |

| Figure 18: MP Configuration Data                         | 36 |

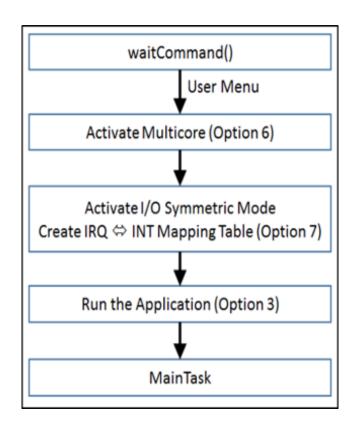

| Figure 19: Wait Command Flow                             | 37 |

| Figure 20: User Menu                                     | 37 |

| Figure 21: Interrupt Mapping Table                       | 38 |

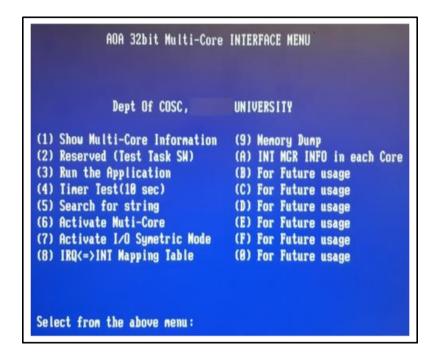

| Figure 22: AP Flow                                       | 40 |

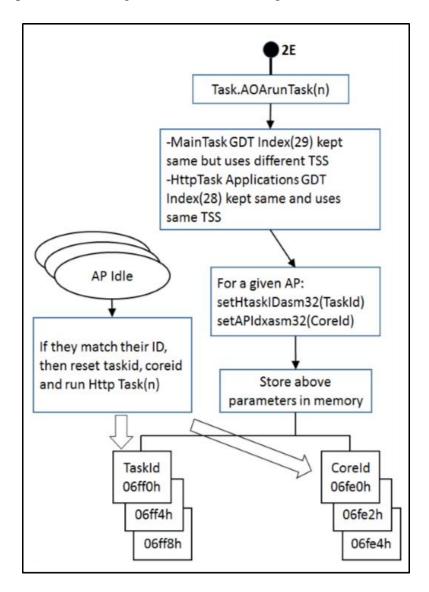

| Figure 23: Initialize LVT                                | 42 |

| Figure 24: AP IDLE Task                                     | 43 |

|-------------------------------------------------------------|----|

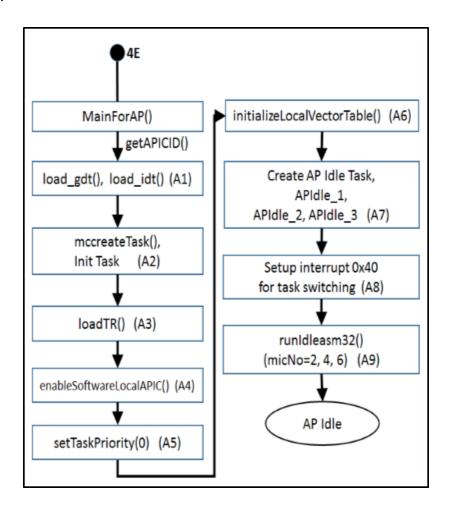

| Figure 25: Scheduling (2E)                                  | 44 |

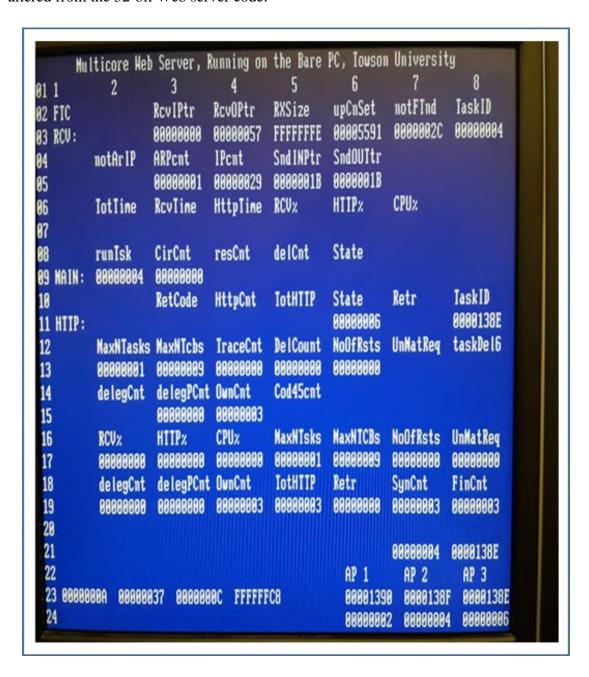

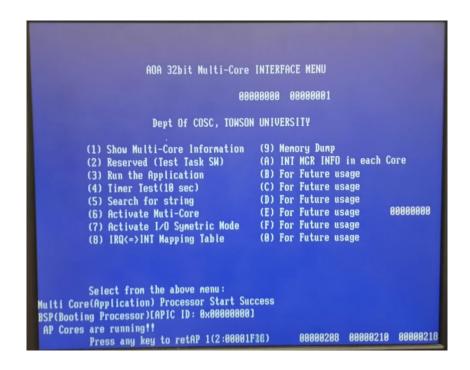

| Figure 26: Multi-core Bare PC Display                       | 46 |

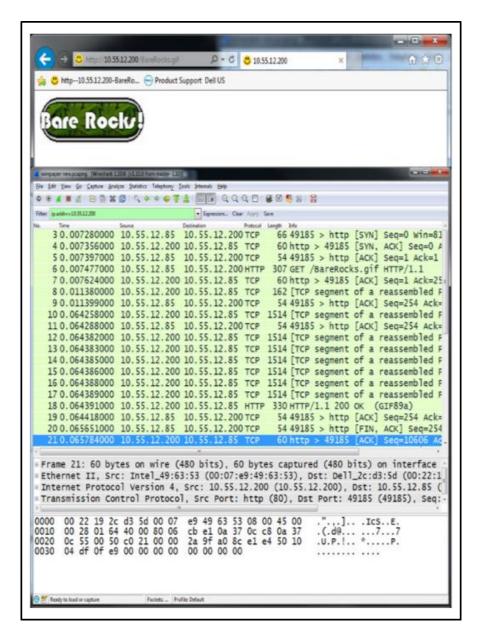

| Figure 27: Multi-core Wireshark Output for a Client Request | 50 |

| Figure 28: BMC Task Structure                               | 54 |

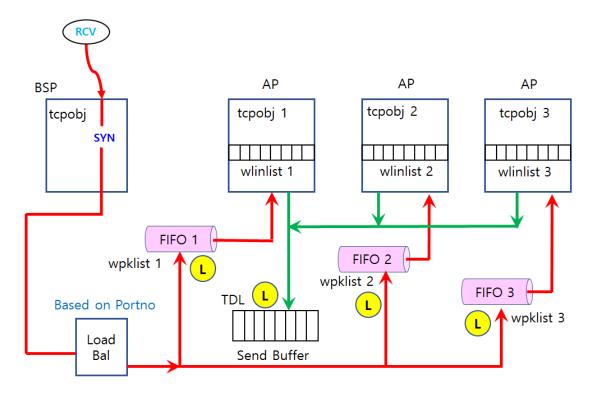

| Figure 29: Multi-core Inter-Process Communication           | 56 |

| Figure 30: Bare PC Structure                                | 60 |

| Figure 31: Assembly compiling batch file                    | 61 |

| Figure 32: C/C++ Compiling Batch File                       | 62 |

| Figure 33: Link Batch File                                  | 62 |

| Figure 34: Make File                                        | 63 |

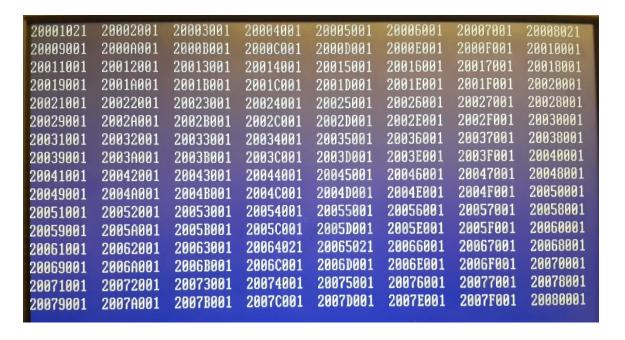

| Figure 35: Memory Dump to debug                             | 64 |

| Figure 36: Bare PC Menu                                     | 65 |

| Figure 37: Load (Option (2))                                | 65 |

| Figure 38: Run Application (Option (3))                     | 66 |

| Figure 39: Changing into Multi-Core Mode (Option (6))       | 67 |

| Figure 40: Activate Multi-Core (Option (6))                 | 67 |

## 1 MOTIVATION

The motivation stems primarily from a need for a 64-bit boot/load/run methodology required for bare PC applications that is part of our mission in the bare machine computing research. Secondly, the current 32-bit bare PC applications developed for x86 architecture can be ported to run on x86-64 architecture in the future. The insight into boot/load/run methodology and its implementation consequently provides a foundation for the development of 64-bit bare PC applications. The methodology presented here also has a broader impact to other pervasive devices and ultimately to the future of bare machine computing paradigm.

#### 2 INTRODUCTION

Bare Machine Computing (BMC) [1] [2] [43] [49] [50] is based on running computer applications on a bare machine without any resident operating system (OS). The BMC programming paradigm differs from a conventional programming paradigm in that the programmer manages all the necessary system resources. This paradigm enables full control of the system via the application software, which directly communicates with and controls the underlying hardware. BMC applications are written in mostly in C/C++ with some use of assembly language (MASM, NASM or TASM) as needed. As described in [59], one or more end-user applications can be written as a single entity referred to as an application object (AO) that runs on a bare machine. Existing BMC applications include Web servers [3] [44], mail servers [4], SIP Servers [5] and VoIP systems [6]. BMC applications can run as multi-threaded programs with thousands of threads and yield high performance with high security as there is no centralized OS or kernel, no external dependencies and no resident mass storage.

Many low-overhead operating systems and kernels have been developed for a variety of environments. For example, Tiny OS is an OS for low-power wireless devices [7]. On the other hand, Kitten is a lightweight high-performance OS that can be used together with Palacios, a virtual machine monitor for applications running in a virtualized environment [8]. The elimination of OS abstractions was originally proposed in [9]. In contrast, the BMC paradigm eliminates all intermediary software providing the combined benefits of improved performance and security.

As newer machines are based on a 64-bit processor and multi-core, 32-bit bare PC applications need to be migrated to the new environment. Many techniques have been proposed for migrating applications to multi-core in an OS environment. In [10], tools for migrating applications to multi-core based on Windows and Linux are surveyed. The use of components and partitions for multi-core migration of legacy real-time systems is described in [11]. In [12], the difficulty of migrating real-time software used in the automotive industry to multi-core is discussed and an approach for developing an automated tool based on static program analysis is suggested.

Migrating bare PC code to run on the 64-bit architecture [47] is not the same as migrating OS-based applications. The primary difference is the absence of any OS or other intermediary software between bare PC applications and the hardware. This means that a bare PC application, regardless of whether it is 32-bit or 64-bit, has to manage its own system resources. We describe the technical details underlying the migration process for a 32-bit bare PC Web server. In particular, we consider design and implementation differences in 32-bit versus 64-bit bare PC applications with a view towards building a tool for automating the migration process in the future.

#### 3 RELATED WORK

## 3.1 Bare Machine Computing Background

The Bare Machine Computing (BMC) paradigm was invented by Dr. Ramesh Karne at Towson University, which was also referred to earlier as a dispersed operating system computing (DOSC) system [13]. The key concepts of the BMC paradigm are as follows:

- 1) Computing applications run in a bare machine without Operating System, centralized kernel, or any system software pre-loaded into the machine.

- 2) The applications can be loaded and carried in a portable device such as flash memory, and run in a bare machine anywhere.

The BMC approach is a novel approach for developing computing applications. Unlike traditional approaches, it is application-centric, and completely differs from conventional computing approaches that are environment and platform-centric. There is little need to upgrade or patch the computing environment often; the focus is on the applications themselves. Once a computing box is made bare, the expense to protect it will be minimized since it only has memory, CPU, a basic user interface (input/output), and a network interface. All persistent data is either stored in a removable device such as USB flash memory or on the network.

In the BMC paradigm, an Application Object (AO) [50] is a self-contained, self-controllable and self-executable unit [2], when an AO is developed, it can be run in any bare hardware such as desktop, laptop, and hand-held, or other electronic device.

| OS-Based System                                      | Bare Machine System                                 |

|------------------------------------------------------|-----------------------------------------------------|

| OS or embedded,                                      | No OS, No embedding,                                |

| Kernel                                               | No Kernel                                           |

| Centralized Control                                  | Application Controlled                              |

| Open Systems                                         | Closed Systems                                      |

| DLLs, Open Ports                                     | No DLLs, No Open Parts                              |

| Some Mass Storage on-board                           | No mass Storage on-board,<br>External Storage       |

| Multiple Modules,<br>Software, other vendor entities | Single application suite or module                  |

| Dynamic Binding                                      | Static Binding                                      |

| Vulnerable to OS and other commercial Software       | No OS or Commercial Software vulnerabilities        |

| General purpose,                                     | Application Centric and                             |

| Multi-user Access                                    | Single User Controlled (User Controlled)            |

| Application depend upon                              | Self-Controlled,                                    |

| other entities during exception                      | Self-managed application                            |

| Many resources to be exploited by intruders          | No valuable resources                               |

| In the box                                           | In the Bare box                                     |

| Virus, worm,, etc. can get in                        | None can get in                                     |

| Leaves execution trace or valuable resource          | None after execution                                |

| Open communication to external users                 | Closed communication                                |

| Open communication to external users                 | to un-intended users                                |

| Box has to be secured                                | Box can be used by any one                          |

| Priv. and user mode                                  | User mode only                                      |

| Other users can access the system while running      | Only intended users can access while running        |

| Internal and a demand of the contract of             | Intruder may get the system go down but cannot      |

| Intruders can damage resources                       | damage any resources                                |

| Needs posting to new environments                    | No posting, runs on any x86(or target) architecture |

| Frequent updates,                                    | No frequent updates,                                |

| Dumping and Waste                                    | no dumping and no waste                             |

| Applications & System Programs                       | Only application programs                           |

Table 1: OS-Based System VS. Bare Machine System

The BMC approach makes computing application simpler and more secure. An AO is developed in a single programming language and run a bare machine, so the AO developer only needs to know one computer language and AO domain knowledge. The AO has no particular ownership and is self-contained and self-executed so that it can run in any bare machine. As the AO controls both application and execution aspects, in addition to

avoiding all the system and kernel related vulnerabilities by making the device bare, it will be more secure. The BMC paradigm changes the way applications are developed today. A summary of comparing conventional applications to BMC applications in Table 1 illustrates the similarities and differences.

## 3.2 BMC Applications

Several complex bare applications have been developed in the bare machine computing laboratory at Towson University, and were the most renowned outcome of doctoral research. They clearly show the feasibility of the BMC paradigm. Long He [3] developed the first bare PC Web server and demonstrated the feasibility of building complex software that runs on a bare PC with thousands of threads and outperforms other compatible commercial Web servers. Gholam Khaksari [6] developed the first VoIP soft-phone that runs on a bare PC and provides secure communication [51] on an end-to-end basis. Andre Alexander [5] built a SIP server and a bare SIP user agent to demonstrate the feasibility of running high performance SIP servers with secure communication using the SRTP protocol. George H. Ford built the first Email server that runs on a bare PC and provides compatible performance to related commercial email servers [4, 14, 15]. Ali Emdadi [16] implemented the complex TLS protocol for a bare Web server. Roman Yasinovskyy [17] [40] implemented the IPv6 protocol for a bare PC VoIP softphone client. Tsetse [55] [57] implemented the Bare PC NAT Box and 6to4 Gateway [56]. IPSec on Bar PC was implemented by Kazemi [58]. Bharat Rawal [18] developed a unique split protocol concept and applied it to Web servers that run on a bare PC. He also developed mini-cluster configurations for Web servers based on the split protocol concept that offer high

performance [19] and run on a bare PC. Patrick Appiah-Kubi developed a secure Webmail server using TLS [20]. Karne [33] developed a USB mass storage device driver for BMC applications. Loukili [53] [54] studied TCP permeance in BMC and Augusto-Padilla [52] studied the possibility of transforming a Linux wireless driver to run on a Bare PC. Okafor [21] demonstrated the feasibility of transforming the SQLite database to run on a bare PC. Alexander [22] [23] showed the applicability of BMC paradigm to handheld devices. Liang [24] and Thompson developed FAT32 file systems [25] [26] that run on bare PCs. These previous doctoral research projects made possible the discovery of many novel characteristics that are unique to BMC and that would be applicable to future computing applications that run on bare devices.

#### 3.3 Other Related Work

Since the invention of computers over 50 years ago, software complexity has been growing rapidly. The massive growth in computing hardware and software has created unmanageable electronic waste [34]. This is partly because new software cannot work with legacy hardware. Software applications, operating systems, tools and gadgets become obsolete in years-sometimes in months. The operating system size has also increased dramatically. For example, for the Microsoft Windows XP professional version with SP3, the size of OS is over one GB.

Much research has focused on developing small kernels and lean OSs or dedicated applications. Previous and recent work include exterminating OS abstractions [9], Exokernel Applications [28, 29], IO-Lite [35], Palacio [8], Libra [27], bare-metal Linux [38], OS Kit [37], Fluke kernel [30], Sandboxing [31], Factored OS [39], Tiny OS [36],

and fast and flexible networking [32]. However, there are significant differences between the BMC approach and those mentioned above. The BMC approach has abandoned the OS approach completely; instead, the AO, a self-contained unit, manages the CPU and memory. The bare machine computing paradigm is at the extreme end of the spectrum compared to OS based systems and other intermediate lean kernel systems.

As per our knowledge, no work on bare machine multi-core and 64-bit applications has been done before.

## 4 INSIGHT INTO x86\_64 BARE PC METHODOLOGY

## 4.1 Overview

Development of bare PC boot/load/run program methodology is not a trivial task. Most of the tools and codes available on the Web require some sort of operating system, kernel, or embedded system. Consequently, the boot process in particular is simpler as the kernel handles complex load and run processes as needed during the execution. The traditional OS and kernel programs that are designed to work with x86 and x86-64 architectures are mature, complex and huge. They hide the architectural intricacies and complexity inside the kernel; thus they are, often overlooked by the application programmer. For a system programmer to work with a complex kernel is a frustrating and a daunting job. In a bare PC application, the application itself manages boot, load and execution of its own program. This poses different challenges and requires the handling of internals of CPU and direct communication with hardware at run time.

## 4.2 Methodology

There are ample amounts of resources and knowledge scattered throughout the Web to construct boot and load programs [42] for conventional platforms that are based on some sort of OS, kernel or embedded systems. As per our knowledge, there are no relevant, useful links, resources, or tools available for bare PC development other than our own research in bare machine computing in the past decade. This section outlines a general overview of this process and the subsequent sections deal with more specific information.

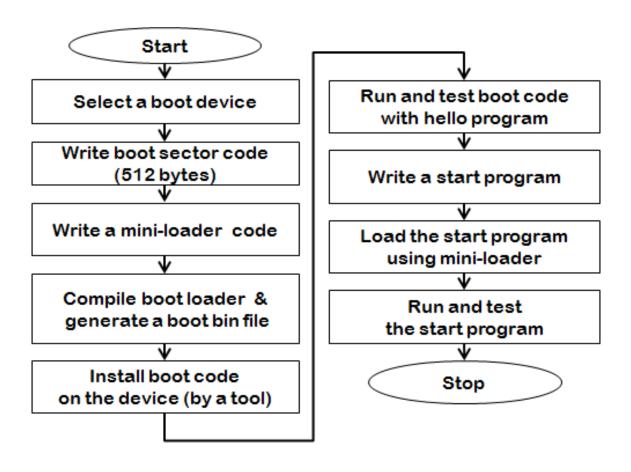

Figure 1: Methodology

Fig.1 shows a generic methodology to illustrate a boot/load/run program process. For a bare PC application, one needs to select a bootable device, which is a detachable mass storage device such as a USB flash drive. A boot sector code and mini-loader that work with a bare PC are needed. The chosen assembler can write this code and compile it to generate a binary file. This bin file is transferred to a bootable USB using a boot install tool. An initial test of boot code can be done by simply printing a "Hello" message after the boot. Once this simple boot test is done, one can write a start program in assembly that can be loaded by the mini-loader (which is part of the boot code). The start program is the beginning of a first program after the boot process.

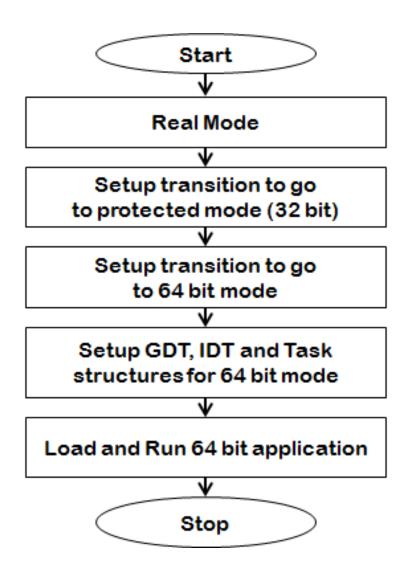

Figure 2: 64-bit Specifics

Fig.2 shows some more details needed to run a 64-bit application. When a PC is booted, it starts in a real mode, which is limited to a 1MB address and has access to all BIOS (Basic Input Output System) interrupts. These interrupts can be used to accomplish simple I/O tasks that are needed during the boot and load process. The start program is used to move from real to protected (32-bit) mode where you have full access to a 4GB address space. In order to transition to 32-bit protected mode, some control registers, GDT and IDT need to be appropriately initialized. Once the 32-bit protected mode is established, you can transition to 64-bit mode which requires a different setting. The 64-bit mode requires setup

for paging, TLB (Translation Look-Aside Buffer), GDT (Global Descriptor Table) and IDT (Interrupt Descriptor Table) entries. Paging is mandatory in 64-bit mode, but optional in 32-bit mode. One can also go directly to 64-bit mode from real mode using the same start program with appropriate setup. A 64-bit application can be loaded, run and tested for its operation once it is in 64-bit mode.

Notice that, as the 64-bit mode supports its previous real and protected modes, the boot/load/run program process for this is more complicated than its predecessors. The transition from one mode to another can be made using interrupt gates or long jump instruction. If we need to use any BIOS calls, we need to go back to real mode from 64-bit mode. Thus, one can design a cycle going from real-protected-64, 64-real, or 64-protected-real modes. In some cases, in a 64-bit mode, if you need to run a 32-bit mode application, you may also choose to go back to 32-bit mode or run it in a compatibility mode. The compatibility mode also requires manipulation of control registers and other structures. The implementation details of this process will be described in later sections. The 64-bit mode and its usage depend upon the need of a user to run strictly 64-bit applications or a mixed set of applications.

## 4.3 BOOT/LOAD/RUN PROGRAM PROCESS

This section describes boot, load and run program process in detail. It also shows the intricacies involved in creating such programs for a bare PC application.

## 4.3.1 Boot Program

A boot program [42] usually consists of a 512-byte (could be more) block of a binary file. It is written in an assembly language and it has a single "text" segment. No data or stack segment is needed to create a working boot program. A boot code needs to be compiled as a binary executable. A variety of compilers such as NASM, MASM, TASM or GAS can be used to create this binary. Note that these assemblers are not compatible in their syntax and structures. A bootable mass storage device such as a hard disk, USB or a CD is used to contain the boot binary in sector 0. For an IBM compatible PC, the boot code on the bootable device is at sector 0, which is loaded into memory at 0x7c00 by its BIOS interrupt upon a power on state. The CPU starts executing this boot code starting at this address. The boot code must contain a 2-byte signature at the end of its 512-byte block (0x55AA). A simple "hello" boot does not have any loader. The "hello" text can be printed using video memory, indicating the success of a boot process.

In IBM compatible PCs, initially video memory can be used to display text on the screen. The video memory start location is at 0xB8000, which can be loaded in the ES segment register to address this memory. To display each character, it requires two bytes to be stored in the video memory, one byte for data and the other byte for the properties. Sophisticated graphics and color patterns require a graphics driver to handle the display and visualization. Simple text and graphics can be done using video memory.

## 4.3.2 Load Program

A detachable mass storage device (USB flash drive) is used to store boot/load application programs and data. There is a mini-loader in the boot program that is simple and limited in its usage due to its size constraints in the boot code. When a boot code is running, the system is in real mode and it has access to BIOS interrupts. The BIOS interrupt 0x13 is used to read all needed sectors from the USB into main memory. The load program requires the starting sector number and the total number of sectors to read from the device. Initially, it reads all sectors needed into memory during initialization and in real mode. If more data is needed to read or write to the USB in protected or 64-bit mode, a device driver and a sophisticated loader are needed for USB. It is also possible to fall back to real mode to read more data using interrupt 0x13 again.

## 4.3.3 Mass Storage and Memory Layouts

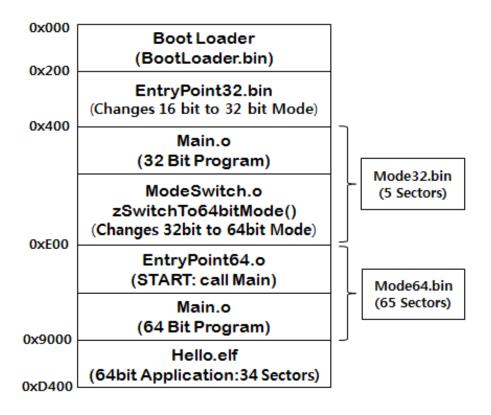

Insight into the boot/load/run program process is illustrated using USB map and memory map figures as shown in Fig. 3 and Fig. 4 respectively. The USB map shows the layout of files that are installed on it in chronological order using a "USB Image Maker" tool, which creates a bootable USB image for bare PC applications. The boot loader (BootLoader.bin) is always installed at sector 0. Sector 1 consists of an entry point code written in assembly (EntryPoint32.bin), which provides a transition from real to protected mode (16 to 32-bit). Entry point code is always loaded in sector 1.

There are three other types of binary files in the USB map as shown in Fig. 3: Mode32.bin, Mode64.bin and Hello.elf. The Mode32.bin file consists of Main.o and

ModeSwitch.o objects including the 32-bit main. The Main.o (first main) object is a 32-bit C program, which demonstrates the transition to 32-bit mode. In addition, it checks available memory and obtains information using get CPUID. The ModeSwitch.o written in assembly provides a transition from 32-bit mode to 64-bit mode. The Mode64.bin consists of EntryPoint64.o and Main.o (second main) objects including the 64-bit main. The EntryPoint64.o is an assembly program that provides an entry point to 64-bit mode. The Main.o (second main) object is a 64-bit C program that demonstrates the transition to 64-bit mode. The Hello.elf is the user application program for 64-bit mode that is installed at the end of all other files. The total number of sectors illustrated in this example include: 106 sectors (1 boot sector, 1 entrypoint sector, 5 Mode32.bin sectors, 65 Mode64.bin sectors and 34 Hello.elf sectors).

Figure 3: USB Layout

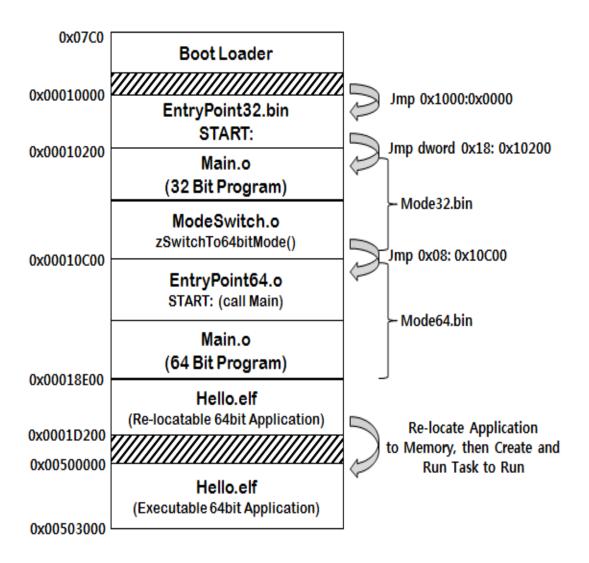

In this given example, 105 sectors are loaded into memory during boot code execution, excluding the boot sector (i.e. 0xD200 bytes). The USB map shows the individual file sizes and their locations. The mini-loader loads all these sectors initially using interrupt 0x13 in real mode.

In this example, the 105 sectors are loaded into memory as shown in Fig. 4. We load these sectors starting above the 1MB address as they can be accessed in protected and 64bit modes. The starting address for EntryPoint32.bin is at 0x00010000. Thus, the boot loader jumps to the START label in this entry point code using a long JMP instruction (jmp 0x1000:0x0000). The ES register is loaded with 0x1000, which translate to 0x00010000, that is the 1MB starting address. At this point, all segment registers have zero values. The entry point code setup transition from real to protected mode and then jumps to a C program main() using another long JMP instruction (**jmp dword 0x18:0x10200**). The GDT entry setup for this Main.o code is 0x18 (0x18/8 = 3), which is a  $3^{rd}$  entry in the table. The Main.o object invokes ModeSwitch.o object, which sets up the 64-bit mode using zSwitchTo64bitMode() function. After the 64-bit mode, setup it jumps to EntryPoint64.o START label using a long JMP instruction (jmp 0x08:0x10c00). GDT entry setup for Mod64.bin code is 0x08 (0x08/8 = 1), which is a 1<sup>st</sup> entry in the table. The 0<sup>th</sup> entry in the GDT table is defined as a null GDT. This entry point code will call a 64-bit program Main.o (second main) which provides a user menu to load and run a 64-bit application. This is part of Mode64.bin as shown in the memory map.

The user menu helps to load and run the "Hello.elf" application. Initially, the "Hello.elf" application was loaded in memory at location 0x00018e00 during the boot time. When this application is actually loaded by user in a 64-bit mode, it may be relocated to other part of the memory such as 0x500000, as illustrated in the memory layout. In a bare PC setup, usually memory map is designed and controlled by the AO programmer and usually it is a fixed location to load a given AO. However, a given AO can have a set of applications constituted as a single user AO.

Figure 4: Memory Layout

## 4.3.4 USB Image Maker

We built a "USB Image Maker" [41] tool using a C program that runs on Linux. This tool uses a "makefile" to compile its code using some input options. The tool uses all the binary and boot images as shown in Fig. 3. To install them on the USB, we use Win32DiskImager which is a free development software. The USBImageMaker makes the USB bootable image, but the Win32DiskImager creates a bootable USB. The USBImageMaker tool is modified so that the boot record bytes 5, 7 and 9 to pass information to the bare PC programs. Byte 5 shows the total number of sectors including the boot sector (106 sectors), byte 7 indicates the size of Mod32.bin (5 sectors) and byte 9 shows the size of Module64.bin (65 sectors). The size of Hell.elf can be derived with the above parameters. This tool can also be used to pass many other parameters to the bare PC application. Notice that the bare PC boot image is not same as other OS boot images and the unused bytes in the boot image can be used as parameter space. The bare PC boot image is also not compatible with other OS boot images. Most of the code used for this tool is off-the-shelf [41] and some modifications are made to suit our bare PC development environment. More details of this tool are not covered in this paper due to space constraints.

## 4.4 BOOT/LOAD/RUN IMPLEMENTATION AND API

This section shows some internal details of implementation and some generic API that can be used to build your own 64-bit bare PC applications [48]. Fig. 5 shows the entry point code (EntryPoint32.s), which is invoked from the boot loader as shown in Fig. 4. The snippets of assembly code are shown in Fig. 5 to illustrate the steps implemented in this program. It uses BIOS interrupt to set A20 bit, which is needed to transition to higher

memory above 1MB. It initializes GDT register and loads control register 0 to go to protected mode. Finally, it uses a long jump to go to Main.o (first main) located at 0x10200 and GDT entry 0x18 (3rd entry).

Figure 5: EntryPoint32

```

//print a string on display

void zStringLinePrint(int cX, int cY, const char* cptrString);

//check memory size if it is more than 64Mbytes or not

BOOL zCheckEnoughMemory(void);

void zInitializePageTables(void); // Create page table for 64bit(IA-32e) mode

// get CPU-ID, vendor string

zGetCPUID(0x00, &dwEAX, &dwEBX, &dwECX, &dwEDX);

// check up supporting 64 bit or not

zGetCPUID(0x80000001, &dwEAX, &dwEBX, &dwECX, &dwEDX);

// switch mode 32 bit to 64 bit, then jump to 64bit(IA-32e) mode

```

Figure 6: Main.c (first Main())

Written in C, the Main.c (first main) in Fig. 6 lists the main steps taken in this program. It creates a page table for 64-bit mode and uses CPUID instruction to obtain the vendor-id

and 64-bit mode supportability feature. Finally, it calls zSwitchTo64bitMode() assembly call that is located in EntryPoint64.s.

<Entrypoint64.s> mov ax, 0x10; set 64 bit mov ds, ax ; DS moves, ax ; ES mov fs, ax ; FS mov gs, ax ; GS ; stack for 64bit mode ; with 1MB size mov ss, ax ; SS mov rsp, 0x6FFFF8 : set RSP mov rbp, 0x6FFFF8 ; set RBP call Main ; 64 bit main ; program

Figure 7: Entrypoint64.s (64-bit Entrance assembly code)

The EntryPoint64.s program written in assembly is shown in Fig. 7. It initializes data segments with GDT selector 2 (0x10 = 16/2 = 2). It initializes the stack and calls Main program (this is the second main) in Fig. 8.

The EntryPoint64.s program written in assembly is shown in Fig. 7. It initializes data segments with GDT selector 2 (0x10 = 16/2 = 2). It initializes the stack and calls Main program (this is the second main).

```

<Main.c(second main())>

void zInitializeConsole(intiX, intiY);

void zGetCursor(int *piX, int *piY );

void zSetCursor(intiX, intiY );

void zInitializeGDTTableAndTSS( void );

void zLoadGDTR( QWORD qwGDTRAddress );

void zLoadTR( WORD wTSSSegmentOffset );

void zInitializeIDTTables( void );

void zLoadIDTR( QWORD qwIDTRAddress);

zCheckTotalRAMSize();

zInitializePIC();

zMaskPICInterrupt(0);

zEnableInterrupt();

TCB* zCreateTask(...);

void zInitializeKeyboard(void);

BYTE zGetCh(void);

void zClearScreen(void);

void zMenu(void);

void zWaitCommand(void);

void zChoiceToStopTask(void);

int zMemDump(void);

```

Figure 8: Main.c (second main() for 64-bit)

Most of the API shown in this figure is self-explanatory. Some important interfaces are shown in Fig. 9 with some key details. The zInitializeGDTTableAndTSS() function updates 64-bit GDT with new parameters required in 64-bit mode. It initializes TSS for 64-bit, which is different from 32-bit mode. The zLoadGDTR() function loads the GDT register with new GDT table. The zLoadTR() function loads the task register. The zInitializeIDTTable() initializes the IDT table. A sample IDT entry for keyboard is shown to illustrate this API. Notice that the keyboard IDT entry is pointing to 0x08 which is a 64-bit mode code segment descriptor. The zLoadIDTR() function initializes IDT table and loads IDT register. Only one IST (interrupt stack table) is used in our demonstration, which is used to create and run one 64-bit mode application. In 64-bit mode, task switching is

done in software, whereas in 32-bit mode, it is done in hardware. The details of task management are not shown in this paper due to space limitations. All the functions described in this section illustrate a common API that can be used to construct boot/load/run programs for any x86-64 based bare PC applications.

## <more details of selected interfaces> void zInitializeGDTTableAndTSS(void); Update 64 bit GDT Code and Data (0x08, 0x10) The new entries reflect 64 bit needs Initialize TSS for 64 bit (it's different from 32 bit) void zLoadGDTR( QWORD qwGDTRAddress ); lgdt [ rdi ] rdi contains GDT table address void zLoadTR( WORD wTSSSegmentOffset ); - ltr di di contains TSS segment(16 bytes) descriptor offset void zInitializeIDTTables(void); create IDT table add IDT entries (e.g. Keyboard: zSetIDTGate( &( ptrIDT[ 33 ] ), kISRKeyboard, 0x08, IDT FLAGS IST1, IDT FLAGS PGR, IDT TYPE INTERRUPT ); ) void zLoadIDTR( QWORD qwIDTRAddress); 0x08 is for entry of GDT code lidt [rdi] rdi contains IDT table address only one IST table used(IST1)

Figure 9: Selected Interfaces Details

#### 4.5 FUNCTIONAL OPERATION AND TESTING

The application program, boot and loader is installed in a USB (mass storage device). This USB can be used to boot/load/run on any x86-64 compatible PC without any hard disk or OS. We used a 2GB Verbatim USB and a 64-bit Laptop (ASUS N43S Intel Core

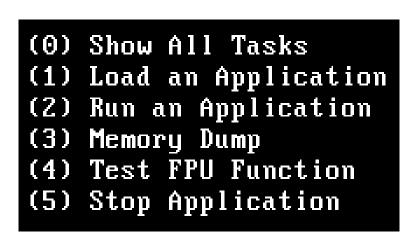

i5, 3rd generation CPU) to test this boot/load/run program process. When the power is turned on, it boots, loads its 64-bit application and runs the application. When it is booted, it starts in real mode and moves into protected and subsequently to 64-bit mode to run the application. When the system transitions to 64-bit mode, it provides a user interface (menu) to load a 64-bit application and runs. It also provides a menu option to dump memory contents for debugging purposes. We have tested a small 64-bit application program using this boot/load/run program process. This system can be expanded to run any set of applications and other features. The snap shots of the running process for the 64-bit "Hello" program are shown in Fig. 10 thru Fig. 12. The Fig. 10 shows the menu interface, Fig. 11 shows the hello program display, and Fig. 12 shows the trace produced by the USB Image Maker tool.

Figure 10: Menu Interface

## Hello, Welcome 64-bits world!!

Figure 11: Application Output

```

./UsbImageMaker.exe 00.BootLoader/BootLoader.bin 01.Mode32

/Mode32.bin 02.Mode64/Mode64.bin 04.Application/hello.elf

[INFO] Copy boot loader to image file

[INFO] File size is aligned 512 byte

[INFO] 00.BootLoader/BootLoader.bin size = [512]

and sector count = [1]

[INFO] Copy protected mode program to image file

[INFO] File size [2690] and fill [382] byte

[INFO] 01.Mode32/Mode32.bin size = [2690]

and sector Count = [6]

[INFO] Copy IA-32e mode program to image file

[INFO] File size [32948] and fill [332] byte

[INFO] 02.Mode64/Mode64.bin size = [32948]

and sector count = [65]

[INFO] Copy 64bit Application to image file

[INFO] File size [17256] and fill [152] byte

[INFO] 04.Application/hello.elf size = [17256]

and sector count = [34]

[INFO] Start to write all information

[INFO] Total sector count except boot loader [105]

[INFO] Total sector count of

protected mode program [6]

[INFO] Total sector count of 64-bit application [34]

[INFO] Image file create complete

```

Figure 12: Image Maker Trace

## 4.6 NOVEL FEATURES

This work presents a complete methodology of creating a boot program, loading application into memory and running a program without any need for an operating system, kernel, or embedded system. There is no middleware required other than the application itself. The CPU structures GDT, IDT, TSS, Video Memory, Keyboard and Display are directly controlled by the application object programmer. This programmer has a complete knowledge of application at static and run time. There is no commercial or vendor software involved in this software engineering paradigm. An end user application suite can be carried on a mass storage device and run anywhere on a bare PC. The direct hardware

control and interfaces (API) shown in this paper provide a complete overview to construct a standalone 64-bit application. Eventually, this API implementation can be moved into the processor chip thus making it intelligent and providing direct access to the programmer. We can eventually make this API standard across many pervasive devices to create portable applications that run on many pervasive devices. When hardware devices are made bare, they can be placed anywhere without concern for computer protection other than physical damage or vandalism.

#### 4.7 SUMMARY

This presents a novel methodology to write bare PC applications that are independent of any operating system, kernel, or embedded system. It described internal details of implementation for boot, load and run process for a 64-bit application. These detailed code snippets and prototypes can be used to implement your own system to create bare PC applications. It also showed its functional operation and testing of a boot/load/run program process. Some significant contributions of this paper, which have a broader impact in developing future bare PC or machine applications, have been identified.

## 5 MIGRATING A WEB SERVER TO A MULTI-CORE ARCHITECTURE

## 5.1 BASIC ISSUES IN MIGRATION

The original bare PC Web server application [3] was written in Visual Studio 10 using C/C++ (32-bit) code and some MASM (Microsoft assembler) code. It also used TASM (Turbo assembler) and NASM (Netwide assembler) code for startup and boot code. The server ran on a single CPU x86 desktop (Dell Optiplex 520) with no paging and no hard disk. A USB flash drive was used to store the entire application (boot, startup and application code including data). In order to migrate the 32-bit code to run on an x86\_64-bit multicore desktop (Dell Optiplex 9010) [47], the first attempt was to run the original server code without changes. Several issues were identified, some of which are discussed below.

### (1) Static Variables

Static variables had incorrect values in them (stored in BSS(Basic Stack Segment) although the BSS segment was not used in the 32-bit code). This did not appear to cause any problems on the 32-bit machine. Bare PC applications use batch files to compile and link i.e. Visual Studio 10 "/bin" files are used for compilation without any use of header files (or libraries). The problem was fixed by adding a "/MERGE:.bss=.data" option in the link for running on a 64-bit machine. This option merges all data into a single data section.

## (2) Dummy Blocks

The 64-bit machine was found to hang if dummy block braces "{....}" were used (without any conditions preceding). This was not an issue in 32-bit; the braces were simply removed to fix this problem.

## (3) C++ Classes

The same C++ class was compiled in two directories and linked, which should not be the case. Simply renaming the class in one directory solves this problem.

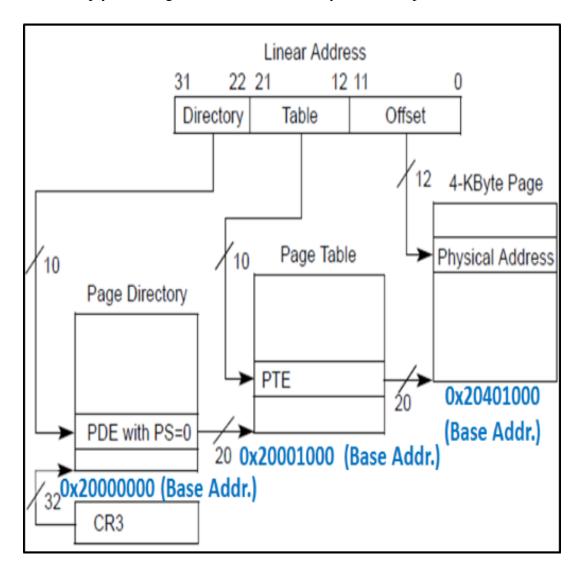

Figure 13: 4K Paging

## 5.2 PAGING AND SINGLE CORE

The 32-bit bare PC code has no paging i.e. the CR0 (control register 0) PG(page) bit and CR4 PAE(page enable) bits are zeros [46] (p.1961). As the Web server is a 32-bit application, paging mode was enabled by setting the CR0 PG bit to 1. This needed to be done before the Web server tasks are created. We therefore created a paging data structure

and initialized the structure with the necessary memory before paging was turned on. The entire Web server executable is 325KB and 1GB of address space is used for the application including code, data and stack. We used a 4K paging scheme and created a data structure as shown in Figure 13. It also shows the actual values used in the PDE and PTE entries. The CR3 is initialized with 0x20000000 (512MB), which is the base address of page directory (PD). This initialization is done in the TSS (task state segment) for the Web server application. There are 1024 entries in PD (there is only one PD in the system). Each PD entry (PDE) points to a separate page table (PT), and there are 1024 PTs. Each page table entry (PTE) points to a page where the offset is used to address the exact location in memory. The paging is managed by the CPU, and software only initializes the data structures. All entries were provided in order to address up to 4GB of memory.

The 32-bit server uses physical memory up to 1GB. This memory is contiguously mapped in our paging structure, thus avoiding page replacement overhead i.e. each logical page is mapped to one physical page. The 32-bit server also uses LDT (Local Descriptor Table) in addition to GDT (Global Descriptor Table). This causes a problem in paging mode as it needs separate paging structures for LDT. We addressed this problem by eliminating LDT and creating new GDTs for paging. As the Web server uses a single address space and there is a single AO running in the bare PC, this paging model is efficient. However, adding paging to the 32-bit code poses some implementation and testing difficulties especially when the entries have wrong values or are not initialized.

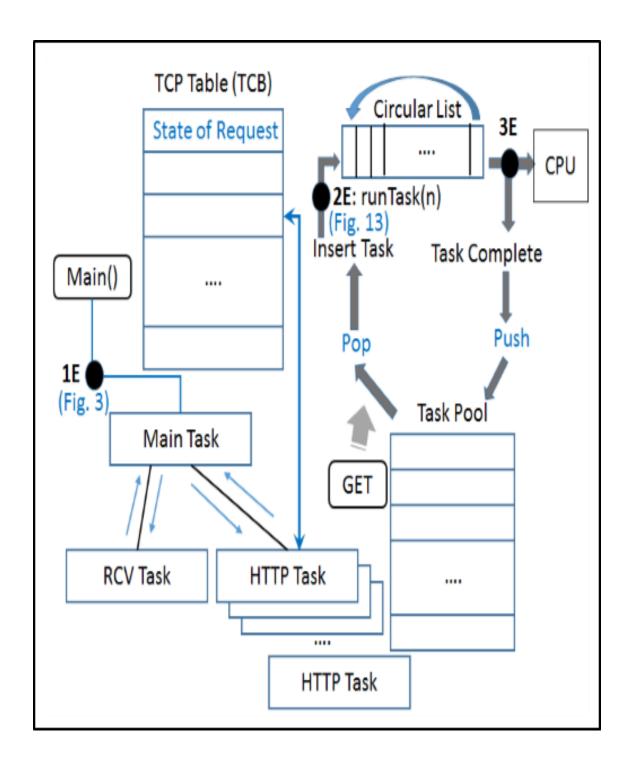

Figure 14: Current Webserver Architecture

Figure 15: BSP Flow (1E)

## 5.3 MULTICORE MIGRATION

Multicore migration poses many challenges in that a bare PC application has to deal with architectural, design and implementation issues in addition to functional operation, testing, and the unique bare PC programming and computing paradigm. A bare PC Web server is

a complex system that differs significantly from its OS-based counterparts. Figure 14 shows a high-level view of the bare PC Web server architecture. There is a main task (MTSK), receive task (RTSK) and several http tasks (HTSK). The MTSK is always running in the system. When a packet arrives, the RTSK runs as a single thread of execution. The RTSK processes packets as they arrive and updates a table that keeps track of TCP parameters and state (known as the TCB). Each entry in the TCB maintains the status of its corresponding client request from start to finish. A task pool is created and stored in advance in a stack to serve client requests. When a client's HTTP Get request arrives, an existing task from the task pool is popped and inserted into a circular list. When this task is complete, it is pushed back onto the stack for reuse. The 32-bit server can run over 6000 concurrent tasks on a single core Dell Optiplex 260 [19]. The code size is about 636 sectors, which is the entire AO needed for the application. The server is designed strictly as a Web server and only performs HTTP requests, which provides protection against conventional attacks that require an OS and other functionality.

#### 5.3.1 BSP Flow

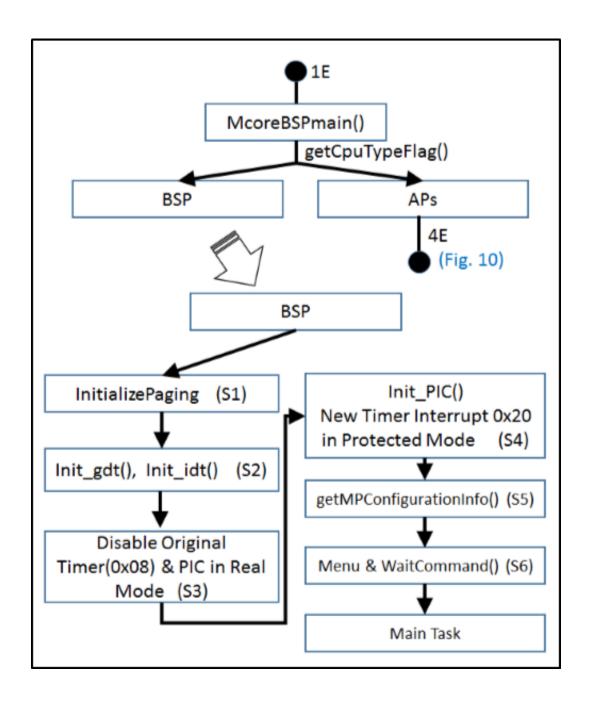

The Web server executable has two separate executables. The first is prcycle.exe (PEX), which has the boot, load and startup code. PEX loads and runs the second executable, test.exe (TEX), which is the Web server application. The display menu enables a user to load, run and debug programs. The Optiplex 9010 uses a quadcore 64-bit processor model. These cores play different roles in the bare PC Web server. The first core is referred to as a boot strap processor (BSP); the other three cores are known as application processors (AP1, AP2, and AP3). Initially, BSP runs the boot code and loads the Web server

application executable. The BSP is automatically configured to run by BIOS (basic input/output system) and APs are not enabled at boot time. In the boot loader code, we set a CPU flag (0x01) at location 0x7c00 (boot address) to identity BSP as a boot processor for the Web server system. When BSP recognizes its role, it resets the CPU flag (0x00) at location 0x7c00 before activating APs.

BSP begins execution at an entry point main(), which is same in the 32-bit Web server code. Figure 14 shows this entry point and also an extension point "1E." This extension point shows the additional code needed for migration (shown in Figure 15). The entry point in BSP starts with the McoreBSPmain() function. This reads the CPU type flag (using getCpuTypeFlag()) as stored in the boot sector, and identifies itself as a BSP processor as described above. The BSP calls InitializePaging() to create and initialize paging data structures (S1). The 32-bit Web server used GDT, LDT and IDT (interrupt descriptor table) entries that were implemented in PEX using TASM code. These entries work only in real mode and the Web server code has interrupt gates to transfer between real and protected modes (real<>protected). Thus, TEX runs in protected mode and PEX runs in real mode. In order to reach hardware interfaces, it uses (real<>protected) mode cycle which serves as a bridge between these two modes.

| Base (H)                                               | Limit (H)                              | D DPL S                             | Туре                               | Base (M)                        | Base (L)                                       | Limit (H)                              |     |

|--------------------------------------------------------|----------------------------------------|-------------------------------------|------------------------------------|---------------------------------|------------------------------------------------|----------------------------------------|-----|

| (1 byte)                                               | (1 byte)                               | (4 bits)                            | (4 bits)                           | 1byte                           | 2bytes                                         | 2bytes                                 |     |

| 0x00                                                   | 0x00                                   | 0x8                                 | 0x9                                | 0x00                            | 0x0a40                                         | 0x006f                                 | Old |

| 0x19                                                   | 0x00                                   | 0x8                                 | 0x9                                | 0x20                            | 0x0000                                         | 0x0068                                 | BSP |

| 0x19                                                   | 0x00                                   | 0x8                                 | 0x9                                | 0x20                            | 0x0068                                         | 0x0068                                 | AP1 |

| 0x19                                                   | 0x00                                   | 0x8                                 | 0x9                                | 0x20                            | 0x00d0                                         | 0x0068                                 | AP2 |

| 0x19                                                   | 0x00                                   | 0x8                                 | 0x9                                | 0x20                            | 0x0138                                         | 0x0068                                 | AP3 |

| 3<br>Handler Offset                                    |                                        | e Reserved                          | Handl                              | er Code                         | Handler Offse                                  |                                        |     |

| Handler Offset<br>(H)                                  |                                        |                                     | Handl<br>Sel                       | ector                           | (L)                                            | t INT                                  |     |

| 3<br>Handler Offset                                    | P DPL Typ                              | e Reserved                          | Handl<br>Sel<br>(2 b               |                                 |                                                |                                        |     |

| Handler Offset<br>(H)<br>(2 bytes)                     | P DPL Typ<br>(1 bytes)                 | e Reserved<br>(1 bytes)             | Handl<br>Sel<br>(2 b               | ector<br>bytes)                 | (L)<br>(2 bytes)                               | INT                                    | Old |

| Handler Offset<br>(H)<br>(2 bytes)<br>0x0000           | P DPL Typ<br>(1 bytes)                 | Reserved<br>(1 bytes)               | Handl<br>Sel<br>(2 b<br>Oxi        | ector<br>pytes)<br>0098         | (L)<br>(2 bytes)<br>0x0167                     | INT Timer(0x08) KeyBoard               | 1   |

| Handler Offset (H) (2 bytes) 0x0000                    | P DPL Typ<br>(1 bytes)<br>0x8f         | e Reserved<br>(1 bytes)<br>0x00     | Handl<br>Sel<br>(2 b<br>Oxi        | ector<br>bytes)<br>0098<br>0138 | (L)<br>(2 bytes)<br>0x0167<br>0x0000           | Timer(0x08) KeyBoard (0x09)            | Old |

| Handler Offset<br>(H)<br>(2 bytes)<br>0x0000<br>0x0000 | P DPL Typ<br>(1 bytes)<br>0x8f<br>0x8f | e Reserved (1 bytes) 0x00 0x00 0x00 | Handl<br>Sel<br>(2 b<br>Oxi<br>Oxi | ector<br>pytes)<br>0098<br>0138 | (L)<br>(2 bytes)<br>0x0167<br>0x0000<br>0x0b45 | Timer(0x08) KeyBoard (0x09) NIC (0x73) | Old |

Figure 16: GDT, IDT

IDT entries are used to address interrupt service routing and GDT entries are used to address the application's code, data and stack. In order to migrate the 32-bit code, we need to implement new GDT and IDT entries and eliminate LDT (new processors use protected mode GDT and IDT structures). Also, PEX is written in TASM (64-bit compilers do not support this assembler). Thus, new GDT and IDT entries were created and initialized using the init\_gdt() and init\_idt() functions (S2). Figure 16 shows sample GDT and IDT entries used in the system to illustrate migration. The new GDT and IDT entries can be used in protected mode, which is required for migration. For example, 32-bit Web server code

used a real mode timer interrupt at 0x08, whereas the new code uses 0x20 interrupt in protected mode. The PIC (programmable interrupt controller) chips have to be disabled (S3) and new APIC (advanced PIC) [45] (p.25) have to be enabled for migration (S4).

```

typedef struct _MPFLOATINGPOINTER

char vcSignature[ 4 ];

DWORD dwMPConfigurationTableAddress;

BYTE bLength;

BYTE bRevision:

BYTE bCheckSum;

BYTE vbMPFeatureByte[ 5 ];

MPFLOATINGPOINTER;

typedef struct _MPCONFIGURATIONTABLEHEADER

char vcSignature[ 4];

WORD wBaseTableLength;

BYTE bRevision;

BYTE bCheckSum;

char vcOEMIDString[ 8 ];

char vcProductIDString[ 12 ];

DWORD dwOEMTablePointerAddress;

WORD wOEMTableSize;

WORD wEntryCount;

DWORD dwMemoryMapIOAddressOfLocalAPIC;

WORD wExtendedTableLength;

BYTE bExtendedTableChecksum;

BYTE bReserved:

} MPCONFIGURATIONTABLEHEADER;

typedef struct _PROCESSORENTRY

BYTE bEntryType;

BYTE bLocalAPICID;

BYTE bLocalAPICVersion;

BYTE bCPUFlags;

BYTE vbCPUSignature[ 4];

DWORD dwFeatureFlags;

DWORD vdwReserved[ 2 ];

PROCESSORENTRY;

```

Figure 17: MP Configuration Structure

The next step in the migration process is to obtain multiprocessor (MP) configuration information [45] (p.37) (S5). This is implemented in the getMPConfigurationInfo() function. This information gathering can be done in many ways [45] (p.38). The MP configuration information is used to manage APs and interrupts. The basic information

stored in the MP configuration includes PIC mode, virtual wire mode via local APIC, virtual wire mode via I/O APIC, and I/O symmetric mode. The information is stored in the Extended BIOS memory area in many places as it is accessed by a floating pointer structure. It is necessary to obtain the MP Floating Pointer Structure Address (e.g 0x000fda10, \_MPFLOATINGPOINTER), which can be found in one of the three places in memory: (1) first KB of extended BIOS data area (EBDA), (2) within the last KB of system memory (639K-640K for 640K systems and 511K-512K for 512K systems), or (3) BIOS ROM address between 0f0000h and 0fffffh. As the information is "floating" in the above areas, we need to search those areas with a signature \_MP\_ to obtain the information.

In the system used for migration, we found this address in the EBIOS memory area. Using this address, we accessed the MP Configuration Table address (for example, the 0x000fd6d0, \_MPCNFIGURATIONTABLEHEADER). The MP floating pointer structure in this system requires use of the MP configuration table instead of the default MP configuration, and virtual wire mode support instead of PIC mode. The first processor entry structure address can be obtained by adding 0x2c to the MP Configuration Table address (0x00fd6d0), i.e. 00fd6fc. The subsequent processor entries can be found by adding another 20 bytes for each entry. The processor parameters listed in the \_PROCESSORENTRY are used to identify a given processor complex and configuration. Figure 17 shows the MP configuration table data structures, and Figure 18 shows the snapshot for the output of accessing these data structures in the current implementation. The processor parameters obtained in this step are used to manage multi-cores in the system including interrupt vectors and control. The MP configuration structures are complex and suited for

conventional OS-based systems as they use system calls and other libraries. Managing these structures in a bare PC, which uses the bare machine computing paradigm, is non-trivial and requires thorough understanding of the intricacies of 64-bit architecture and multi-core architecture to migrate 32-bit applications.

```

MP Configuration Table Sunnary

MP Configuration Table Analysis Success

MP Floating Pointer Address : 0x000FDA10

PIC Mode Support : NO

MP Configuration Table Header Address : 0x000FD6D0

Base MP Configuration Table Entry Start Address : 0x000FD6FC

Tatal Number of Cores/Processors: 4

ISA Bus ID : 0x3

------ MP Floating Pointer -----

Signature : _MP_

MP Configuration Table Address : 0x000FD6D0

Length : 1 * 16 Bytes

Version: 4

CheckSun : 0xEB

Feature Byte 1 : 0x0

(Use MP Configuration Table)

(Virtual Wire Mode Support Instead of PIC Mode)

Feature Byte 2 : 0x0

----- MP Configuration Table Header (1/2)-----

Signature : PCMP

Length: 700 Bytes

Version: 4

CheckSun : 0xDD

Press any key to continue... ('q' is exit) :

----- MP Configuration Table Header Continue.

OEM ID String : CBX3

Product ID String : DELL

OEM Table Pointer : 0x0

OEM Table Size : 0

Butes

Entry Count : 76

Menory Mapped I/O Address Of Local APIC : FEE00000

Extended Table Length : 124 Byte

Extended Table Checksum : 0xB2

Press any key to continue... ('q' is exit) :

```

Figure 18: MP Configuration Data

Figure 19: Wait Command Flow

Figure 20: User Menu

```

----- IRQ To I/O APIC INT IN Mapping Table ------

PIC Controller

Muliti Core Int Controller

Timer IRQ to INTIN

PS2 KB IRQ to INTIN

Slave PIC IRQ to INTIN

INTIN [255]

COM2 IRO to INTIN

COM1 IRQ to INTIN

LPT2 IRQ to INTIN

Floppy Disk IRQ to INTIN

LPT1 IRQ to INTIN

RTC IRQ to INTIN

IROC9 ] -> INTIN C9 ]

Reserved IRQ to INTIN

Not Used IRQ to INTIN

Not Used IRQ to INTIN

PS2 Mouse IRQ to INTIN

IRO[13] -> INTIN [13]

CoProcessor IRQ to INTIN

IRQ[14] -> INTIN [14]

HDD1 IRQ to INTIN

IRQ[15] -> INTIN [15]

HDD2 IRO to INTIN

Press any key to return to menu...

```

Figure 21: Interrupt Mapping Table

The BSP invokes the waitCommand() function (S6), which provides a sequence of commands to run an application as shown in Figure 19. This function provides a user interface to start and debug applications. The actual menu screen is shown in Figure 20. This menu allows a user to activate multicore and I/O symmetric mode (options 6 and 7 respectively), map IRQs to the interrupt table (8), and run the application (option 3). Each processor has its own APIC to control interrupts. The interrupt requests come to an I/O APIC controller, which will be delegated to each processor APIC. Thus, to activate multicore (option 6), the BSP performs two steps. The first step involves reading the MSR register using the "rdmsr" assembly instruction, ORing with the 0x800 value and writing back using the "wrmsr" assembly instruction. In the second step, it activates its own local APIC by changing the spurious interrupt vector register (0xfee00000 (base) + 0xf0 (offset))

with a value 0x100 [45] (p.77). At this point, interrupts are directed to only the BSP. In order to direct interrupts to other APs, we need to activate I/O symmetric mode (option 7). In symmetric mode, it is not possible to use virtual wire mode interrupt routing [45] (p.85).

The MP configuration table must be set up to do appropriate interrupt routing to APICs. This implementation is complex and depends on the APIC architecture and interrupt load balancing. In this system, timer interrupts are directed to APs and all other interrupts are processed by the BSP. The I/O APIC controller IRQ to INTIN map is shown in Figure 21. This map is derived as part of option 7 and also uses the MP configuration table. This map helps to identify interrupt numbers and provides the appropriate interrupt code to process. Finally, when run (option 3) is chosen, the BSP creates MTSK and starts executing that task. At this point, the BSP is in MTSK and all other APs are activated and running their individual idle tasks.

#### 5.3.2 AP Flow

The BSP takes over the boot process and loading of an application as the boot code had 0x01 in its first byte. When the BSP entered main(), it checked for this flag and took the BSP flow as shown above. When the BSP turns off this flag, all APs are ready to enter main(). Each AP will also go through the McoreBSPMain() function (Figure 15), but they then discover that getCpuTypeFlag() returns a zero value. Thus, they take the AP Flow path as shown in Figure 22. The AP Flow is as complex as the BSP Flow. An AP enters the MainForAP() function and gets its ID by invoking getAPCID(). The ID is stored in the PROCESSORENTRY structure at an offset of 4. The data structures as shown in the MP

configuration [45] (p.37) allow us to compute the address for each core and its related PROCESSENTRY to access the core id. In our system, the IDs for APs are 0, 2, 4 and 6. Figure 18 shows these IDs and the rest of the parameters read from the MP configuration structures.

Figure 22: AP Flow

Each AP needs GDT and IDT tables to work with the Web server application. These tables are initialized before by the BSP using the init\_gdt() and init\_idt() functions (A1). In this case, we simply load the entries by using the functions load\_gdt() and load\_idt(). All processors have access to all resources of the Web server as they are running a shared memory multi-processor model. The AP then creates an initial task by using mcreateTask()

(A2). The loadTR() function will load the TR (task register) to prepare to run a task (A3). The enableSoftwareLocalAPIC() function will activate its own local APIC by changing the spurious interrupt vector register (0xfee00000 (base) + 0xf0 (offset)) with a value 0x100 (A4) [45] (p.75~87). The setTaskPriority(0) function will set zero value in task priority register (0xfee00000(base) + 0x80 (offset)) to disable processing interrupts in the AP (A5).

The initializeLocalVectorTable() function (A6) [45] (p.75~87) is difficult to implement due to its complexity. The actual code is shown in Figure 23. This function has seven intricate steps needed to set up interrupt capabilities for the core. Step 1 sets up the base address, which is derived from the MP configuration table (i.e. 0xfee00000). Step 2 blocks the timer interrupt by setting the mask value 0x010000 into the LVT (local vector table) timer register with an offset of 0x320 (i.e. address 0xfee00320). Step 3 is used to block LVT0 interrupt, for which its register address is located at (0xfe000350). Step 4 is used to setup this interrupt as NMI (non-maskable) interrupt, for which its register address is located at (0xfe000360). Step 5 is used to block the error interrupt for which its register address is located at (0xfe00370). Step 6 is used to block the performance monitoring interrupt, for which its register address is located at (0xfe000340). Finally, Step 7 is used to block the temperature sensor interrupt, for which its register address is located at (0xfe000330). We blocked most of the interrupts in the AP to facilitate and debug multicore processors. In a completely migrated system, these interrupts must be enabled and handled accordingly to capture errors and other issues relevant to a high-performance system.

```

void initializeLocalVectorTable( void )

DWORD dwLocalAPICBaseAddress, dwTempValue, dwSetVal;

// Step 1.

dwLocalAPICBaseAddress = zGetLocalAPICBaseAddress();

// Step 2.

dwSetVal=getcmpaddrasm32(dwLocalAPICBaseAddress +

APIC REGISTER TIMER);

setLocalAPICasm32(dwLocalAPICBaseAddress +

PIC REGISTER TIMER, dwSetVal|APIC INTERRUPT MASK);

dwSetVal=getcmpaddrasm32(dwLocalAPICBaseAddress +

APIC_REGISTER_LINTO);

setLocalAPICasm32(dwLocalAPICBaseAddress +

APIC_REGISTER_LINTO, dwSetVal|APIC_INTERRUPT_MASK);

dwSetVal=getcmpaddrasm32(dwLocalAPICBaseAddress +

APIC REGISTER LINT1);

setLocalAPICasm32(dwLocalAPICBaseAddress +

APIC_REGISTER_LINT1, dwSetVal|APIC_TRIGGERMODE_EDGE |

APIC_POLARITY_ACTIVEHIGH | APIC_DELIVERYMODE_NMI);

// Step 5.

dwSetVal=getcmpaddrasm32(dwLocalAPICBaseAddress +

APIC REGISTER ERROR);

setLocalAPICasm32(dwLocalAPICBaseAddress +

APIC_REGISTER_ERROR, dwSetVal|APIC_INTERRUPT_MASK);

dwSetVal=getcmpaddrasm32(dwLocalAPICBaseAddress +

APIC REGISTER PERFORMANCEMONITORINGCOUNTER);

setLocalAPICasm32(dwLocalAPICBaseAddress +

APIC REGISTER PERFORMANCEMONITORINGCOUNTER,

dwSetVal|APIC INTERRUPT MASK);

// Step 7.

dwSetVal=getcmpaddrasm32(dwLocalAPICBaseAddress +

APIC REGISTER THERMALSENSOR);

setLocalAPICasm32(dwLocalAPICBaseAddress +

APIC_REGISTER_THERMALSENSOR, dwSetVal|APIC_INTERRUPT_MASK);

```

Figure 23: Initialize LVT

Once the interrupts are set properly, we can create an idle task which will run in the AP as a never-ending loop in the processor (A7). We created three idle tasks (APIdle\_1,

APIdle\_2, APIdle\_3) with their own GDT indexes (i.e 0x208, 0x210, 0x218) and their corresponding GDT entries. We have also created one IDT entry for each AP; an interrupt vector 0x40 operates as a task gate to do task switching from init task to idle task (A8).

Figure 24: AP IDLE Task

```

// Step 1. -----

void AOATask::APIdle_1(long z1)

int i, iCoreIDX;

int previous_task;

i=0;

iCoreIDX=0;

previous_task=0;

while(1) {

iCoreIDX=io.AOAgetAPIdxasm32();

i=(int)io.AOAgetHTakIDasm32();

if (previous_task==i)

else{

if (iCoreIDX == 1) //iCoreIDX = index of the APIC ID

io.AOAsetAPIdxasm32(0x00);

io.AOAsetHTakIDasm32(0x0000);

runTask(i);

previous_task=i;

1;

// Step 2. -----

void (_thiscall AOATask::*pFunc1)(long) = &AOATask::APIdle_1;

void* p1Ptr = (void*&)pFunc1;

Function_Address_Array[0] = (int)p1Ptr,

// Step 3 -----

if (micNo==2) //micNo = APIC ID

idlesel=(TASK_GDT_IDLE+io.AOAGetCoreIDX(io.AOAgetAPICID()))*8;

task.AOAmccreateTask((long)Function_Address_Array[0],

(int*)(AP_STACK_BASE_ADDR2+io.AOAgetAPICID()*0x10000),

idlesel, TASK_GDT_IDLE+io.AOAGetCoreIDX(io.AOAgetAPICID()), 0);

io.AOAmsetidtentry(0x40, 0, idlesel, MCATR_TASKGATE);

// Step 4. -----

io.AOArunIdleasm32();

```

Figure 25: Scheduling (2E)

Each AP will run its own idle task and monitor for any tasks assigned to it by the BSP. In order to go to idle task, we need an interrupt 0x40 to do task switching. The idle task will be running and waiting for any future tasks to be assigned by the BSP processor. The runIdleasm32() will enable the task switch from init to idle task by invoking interrupt 0x40. Figure 24 illustrates some details of creating the idle task in the AP. Step 1 in the figure shows the APIdle\_1 function, where there is a never-ending loop to serve BSP requests. The address of this function is captured in Step 2 and stored in an array. Step 3 shows task creation for AP1. In this step, we create a task using the AOAmccreateTask() function, which needs function address as captured in the array, stack address, GDT entry no and task id. We also set up an IDT entry by the AOAmsetidtentry() function that is needed for task switching from init to idle task. Finally, Step 4 shows the invocation of interrupt 0x40 that will switch from init to idle task. The process described above enables AP to go from start to running idle task (A9). Now, each AP is running in their own idle task and they are ready to process the HTTP task requested by the BSP. The while loop in Step 1 compares its own AP identification with the one waiting to run, then takes that HTTP task and runs it using the runTask(i) function.

### 5.3.3 Task Scheduling Flow

This section describes the migratory code added for the Web server at point "2E" in Figure 14. When a Get request arrives from an HTTP client, the server pops an HTTP task (HTSK) from the task pool and inserts it into a circular list. Each request is an independent HTSK that handles data transfer and termination of the task. The connection part of the HTSK is done by RTSK. The MTSK and RTSK run on the BSP only. When there is only

one core, all tasks are in the same processor. Figure 25 shows the task scheduling flow altered from the 32-bit Web server code.

Figure 26: Multi-core Bare PC Display

When a HTSK is ready to be dispatched, it calls the function runTask(n) to run a task with task id n. In order to run task n, we have to do task switching from MTSK to HTSK.

The MTSK GDT index (in the 32-bit server) is 29. The new code uses the same GDT index with a new TSS. In the 32-bit server, HTSK has its own GDT index (28) and its own TSS. The new code uses the same GDT and TSS structures with no change. The task switch logic is not changed for migration. When APs are enabled, for a given AP, we set task id and core id in a shared memory location for each processor, where a core can access its own coreid. setHTaskIDasm32(taskid) and setAPIdx2asm32(coreid) are functions that will store the values in shared memory at 0x06fe0 and 0x06ff0 for core 1. Similarly, for core 2 and core 3, the values are stored in shared memory at different locations. As described before, APs are running in an APIdle loop and check for the match of their coreid in the shared memory. If the coreid matches, the core will invoke runTask(n) to run the HTSK. In a given AP, when the HTSK is complete, it returns back to the idle task.

In the 32-bit Web server, there is only one processor to schedule MTSK, RTSK and HTSK. As shown in Figure 14, "3E" connection point illustrates the new configuration for migration. In this case, we have BSP, AP1, AP2 and AP3 processors connected to the circular list. These execution elements have to be load balanced by the logic shown in Figure 25. In the current model, we do not perform any optimal load balancing techniques, but simply allocate HTSKs to APs in a round robin manner.

This section described many aspects of migration needed for the Web server code to run on multi-core processors in detail. We found that the migration path is complex to implement not only in a bare PC but also in OS environments.

## 5.4 FUNCTIONAL OPERATION AND DATA